US009418027B2

# (12) United States Patent Hadley

## (10) Patent No.: US 9,418,027 B2 (45) Date of Patent: Aug. 16, 2016

#### (54) SECURE BOOT INFORMATION WITH VALIDATION CONTROL DATA SPECIFYING A VALIDATION TECHNIQUE

(75) Inventor: Ted A Hadley, Sunnyvale, CA (US)

(73) Assignee: **Hewlett Packard Enterprise Development LP**, Houston, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/233,334

(22) PCT Filed: Mar. 30, 2012

(86) PCT No.: PCT/US2012/031542

§ 371 (c)(1),

(2), (4) Date: Jan. 16, 2014

(87) PCT Pub. No.: **WO2013/012461**

PCT Pub. Date: Jan. 24, 2013

#### (65) **Prior Publication Data**

US 2014/0189340 A1 Jul. 3, 2014

#### Related U.S. Application Data

- (60) Provisional application No. 61/509,078, filed on Jul. 18, 2011.

- (51) **Int. Cl. G06F 21/78** (2013.01) **G06F 13/16** (2006.01)

(Continued)

- (52) **U.S. Cl.** CPC .....

**G06F 13/1663** (2013.01); **G06F 21/54** (2013.01); **G06F 21/55** (2013.01); **G06F 21/57** (2013.01);

#### (Continued)

#### (58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,183,498 A 4,424,561 A 5/1965 Howe et al. 1/1984 Stanley et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1650183 A 8/2005 CN 1820235 A 8/2006

(Continued)

#### OTHER PUBLICATIONS

"ARM Security Technology Budding a Secure System Using TrustZone® Technology", < http://infocenter.arm.com/help/topic/com.arm.doc.prd29-genc-009492c/PRD29-GENC-009492C\_trustzone\_security\_whitepaper.pdf > Issue: C, 2009.

(Continued)

Primary Examiner — William Powers (74) Attorney, Agent, or Firm — Hewlett Packard Enterprise Patent Department

#### (57) ABSTRACT

Examples disclosed herein relate to secure boot information with validation control data specifying a validation technique. Examples include determining, with the specified validation technique, whether validation data is consistent with the secure boot information.

#### 15 Claims, 5 Drawing Sheets

### US 9,418,027 B2

Page 2

| (51) | Int. Cl.          |                                               | 7,218,567 B1                        |         | Trimberger et al.                  |

|------|-------------------|-----------------------------------------------|-------------------------------------|---------|------------------------------------|

|      | H04L 9/32         | (2006.01)                                     | 7,222,053 B2                        |         | Snyder et al.                      |

|      | G06F 21/54        | (2013.01)                                     | 7,237,121 B2<br>7,265,611 B2        | 9/2007  | Cammack et al.                     |

|      | G06F 21/75        | (2013.01)                                     | 7,299,347 B1*                       |         | Kao 713/2                          |

|      | H04L 9/08         | (2006.01)                                     | 7,299,365 B2                        | 11/2007 | Evans                              |

|      | G06F 1/24         | ` '                                           | 7,305,534 B2                        |         | Watt et al.                        |

|      |                   | (2006.01)                                     | 7,360,073 B1                        | 4/2008  | Billstrom et al.                   |

|      | G06F 21/57        | (2013.01)                                     | 7,398,441 B1                        | 7/2008  |                                    |

|      | G06F 12/14        | (2006.01)                                     | 7,423,529 B2                        |         | Singer et al.                      |

|      | G06F 21/60        | (2013.01)                                     | 7,424,398 B2                        |         | Booth et al.                       |

|      | G06F 21/55        | (2013.01)                                     | 7,457,960 B2                        |         | Kablotsky                          |

|      | G06F 21/72        | (2013.01)                                     | 7,512,719 B1                        |         | Gillespie                          |

|      | G06F 21/79        | (2013.01)                                     | 7,525,836 B2<br>7,549,064 B2        |         | Backus et al.<br>Elbert et al.     |

|      |                   | ` '                                           | 7,568,112 B2                        | 7/2009  | Yamaguchi                          |

|      | G09C 1/00         | (2006.01)                                     | 7,571,475 B2                        | 8/2009  | Moon                               |

|      | G06F 11/22        | (2006.01)                                     | 7,580,919 B1                        |         | Hannel et al.                      |

|      | G06F 21/74        | (2013.01)                                     | 7,657,760 B2                        | 2/2010  | Teramoto et al.                    |

|      | G01R 31/317       | (2006.01)                                     | 7,667,997 B2                        | 2/2010  | Rodriguez                          |

| (52) | U.S. Cl.          | , ,                                           | 7,681,024 B2                        | 3/2010  |                                    |

| (52) |                   | F 21/575 (2013.01); G06F 21/602               | 7,729,156 B2                        |         | Rodriguez et al.                   |

|      |                   | 26F 21/72 (2013.01); G06F 21/74               | 7,733,250 B1                        |         | Tsyrganovich                       |

|      |                   | 06F 21/75 (2013.01); G06F 21/78               | 7,757,098 B2<br>7,761,904 B2        |         | Brannock et al.<br>Hessel et al.   |

|      |                   |                                               | 7,761,904 B2<br>7,774,619 B2        |         | Paaske et al.                      |

|      |                   | 606F 21/79 (2013.01); G09C 1/00               | 7,774,019 B2<br>7,793,067 B2        |         | Kegel et al.                       |

|      |                   | 01); <b>H04L 9/088</b> (2013.01); <b>H04L</b> | 7,831,839 B2                        |         | Hatakeyama                         |

|      | `                 | .01); <b>H04L 9/32</b> (2013.01); G01R        | 7,844,835 B2                        | 11/2010 | Ginter et al.                      |

|      | 31/3              | 1719 (2013.01); G06F 2221/2143                | 7,937,596 B2                        |         | Mackey et al.                      |

|      | (2)               | 013.01); <i>H04L 2209/12</i> (2013.01)        | 7,949,912 B1                        |         | Trimberger                         |

|      |                   |                                               | 7,954,153 B2                        |         | Bancel et al.                      |

| (56) | Refe              | rences Cited                                  | 7,966,467 B1<br>8,027,927 B2        |         | Ludloff et al. Ogg et al.          |

|      |                   |                                               | 8,572,410 B1*                       |         | Tkacik et al 713/193               |

|      | U.S. PATE         | NT DOCUMENTS                                  | 8,621,597 B1                        | 12/2013 |                                    |

|      | 5 121 0 40 4 7/10 | 22 17 1                                       | 8,819,839 B2                        | 8/2014  | Henry et al.                       |

|      |                   | 92 Knapczyk<br>93 Hammond et al.              | 2001/0010086 A1                     |         | Katayama et al.                    |

|      |                   | 93 Alpert et al.                              | 2002/0120851 A1                     | 8/2002  | Clarke                             |

|      |                   | 95 Peters et al.                              | 2002/0129195 A1                     |         | Hongo et al.                       |

|      |                   | 95 Piosenka et al.                            | 2003/0133574 A1<br>2003/0140228 A1  |         | Caronni et al.<br>Binder           |

|      |                   | 95 Finley et al.                              | 2003/0140228 A1<br>2003/0197638 A1  |         | Bloebaum et al.                    |

|      |                   | 95 Junya                                      | 2003/0200453 A1                     |         | Foster et al.                      |

|      |                   | 96 Miller et al.                              | 2003/0200454 A1                     |         | Foster et al.                      |

|      |                   | 96 Masuda                                     | 2004/0078664 A1                     |         | Takahashi                          |

|      |                   | 97 Broadwater et al.<br>97 Roeber et al.      | 2004/0088333 A1                     |         | Sidman                             |

|      |                   | 98 Takahashi et al.                           | 2004/0148480 A1                     |         | Watt et al.                        |

|      |                   | 99 DeRoo et al.                               | 2004/0153593 A1<br>2004/0210764 A1  |         | Watt et al.<br>McGrath et al.      |

|      |                   | 99 Davis                                      | 2004/0210704 A1<br>2004/0267847 A1  | 12/2004 | Harner                             |

|      | · / /             | 99 Ebrahim et al.                             | 2005/0091554 A1                     |         | Loukianov                          |

|      |                   | 00 Shutty et al.                              | 2005/0120216 A1                     | 6/2005  | Lee et al.                         |

|      |                   | 00 Sagi<br>01 Takada                          | 2005/0144358 A1                     |         | Conley et al.                      |

|      |                   | 01 Matyas                                     | 2005/0154903 A1                     | 7/2005  |                                    |

|      |                   | 01 Sutherland                                 | 2005/0235166 A1                     |         | England et al.                     |

|      |                   | 02 Swift et al.                               | 2006/0010356 A1<br>2006/0023486 A1  |         | Snyder et al.<br>Furusawa et al.   |

|      |                   | 02 Collins et al.                             | 2006/0031685 A1                     |         | Chen et al.                        |

|      | ., ,              | 02 Blossfeld et al.                           | 2006/0059345 A1                     |         | Fayad et al.                       |

|      |                   | 02 Drews 713/176<br>02 Goodman                | 2006/0059373 A1                     | 3/2006  | Fayad et al.                       |

|      |                   | 03 Hosoe                                      | 2006/0059374 A1                     |         | Hameau et al.                      |

|      |                   | 03 Hosoe<br>03 Buer                           | 2006/0090084 A1                     | 4/2006  |                                    |

|      |                   | 03 Moyer et al.                               | 2006/0095726 A1                     |         | Zaabab et al.                      |

|      |                   | 04 Kitamura                                   | 2006/0101241 A1<br>2006/0155988 A1* |         | Curran et al. Hunter et al 713/164 |

|      |                   | 04 Duff                                       | 2006/0168212 A1                     |         | Parsons et al.                     |

|      |                   | 04 Willman et al.                             | 2006/0179302 A1                     |         | Hatakeyama                         |

|      | / /               | 04 Brothers et al.                            | 2006/0179324 A1                     |         | Hatakeyama                         |

|      |                   | 04 Elward<br>04 Anderson et al.               | 2006/0184791 A1                     |         | Schain et al.                      |

|      |                   | 04 Anderson et al.<br>05 Dykes et al.         | 2006/0208884 A1                     |         | Diamant                            |

|      |                   | 05 Bykes et al.<br>05 Eslinger et al.         | 2006/0215437 A1                     |         | Trika et al.                       |

|      |                   | 05 Lee et al.                                 | 2006/0225142 A1                     | 10/2006 |                                    |

|      |                   | 06 Kocher et al.                              | 2006/0247873 A1                     |         | Fung et al.                        |

|      |                   | 06 Nagase                                     | 2007/0067644 A1                     |         | Flynn et al.<br>Chambers et al.    |

|      |                   | 06 Miller et al.                              | 2007/0136576 A1<br>2007/0136606 A1  |         | Mizuno                             |

|      |                   | 06 Caronni et al.<br>06 Yoshida et al.        | 2007/0130000 A1<br>2007/0140477 A1  | 6/2007  |                                    |

|      |                   | 00 Toshida et al.<br>07 Tkacik et al.         | 2007/0174909 A1                     |         | Burchett et al.                    |

|      | .,,               |                                               |                                     |         |                                    |

| (56) References Cited        |               | EP                | 1762855                             | A1                                                              | 3/2007<br>8/1989                                                                                                                                                    |          |                      |                  |  |  |

|------------------------------|---------------|-------------------|-------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|------------------|--|--|

| U.S. PATENT DOCUMENTS        |               |                   | DOCUMENTS                           | JP<br>JP<br>JP                                                  | 1201762<br>06-028885<br>08-069697                                                                                                                                   |          | 2/1994<br>3/1996     |                  |  |  |

| 2007/0192610                 | Δ1            | 8/2007            | Chun et al.                         | JР                                                              | 1131068                                                                                                                                                             |          | 2/1999               |                  |  |  |

| 2007/0192828                 |               |                   | Messina et al.                      | JP                                                              | 2008192036                                                                                                                                                          |          | 8/2008               |                  |  |  |

| 2007/0204170                 |               |                   | Oren et al.                         | WO<br>WO                                                        | WO-9745980<br>WO-9931665                                                                                                                                            | Al       | 12/1997<br>6/1999    |                  |  |  |

| 2007/0226494<br>2007/0237325 |               |                   | O'Brien et al.<br>Gershowitz et al. | wo                                                              | WO-2011080841                                                                                                                                                       | A1       | 7/2011               |                  |  |  |

| 2007/0237332                 |               | 10/2007           |                                     |                                                                 | OTHER                                                                                                                                                               | DLID     | LICATIONS            |                  |  |  |

| 2007/0283140                 |               |                   | Jones et al.                        |                                                                 | OTHER                                                                                                                                                               | PUB.     | LICATIONS            |                  |  |  |

| 2008/0005577<br>2008/0005586 |               |                   | Rager et al 713/183<br>Munguia      | Anderso                                                         | n, R. et al., "Crypt                                                                                                                                                | ograpł   | nic Processors—A     | Survey," Pro-    |  |  |

| 2008/0010567                 |               |                   | Hughes et al.                       | ceedings                                                        | of the IEEE, vol. 9                                                                                                                                                 | 4, No.   | 2, Feb. 2006, pp. 3  | 357-369.         |  |  |

| 2008/0072018                 |               |                   | Le et al.                           |                                                                 | Intelligent Sensors                                                                                                                                                 |          |                      |                  |  |  |

| 2008/0112405<br>2008/0137848 |               |                   | Cholas et al.<br>Kocher et al.      |                                                                 | hnologies EMAG,<br>ISSN 1424-8220, Ja                                                                                                                               |          | ,                    | _                |  |  |

| 2008/0162848                 |               |                   | Broyles et al.                      | sensors>                                                        |                                                                                                                                                                     | 111. 22, | 2010. \www.map       | n.com/journal/   |  |  |

| 2008/0165952                 |               |                   | Smith et al.                        |                                                                 | al.; "Calibration of C                                                                                                                                              | On-Chi   | ip Thermal Sensors   | susing Process   |  |  |

| 2008/0172538<br>2008/0183305 |               |                   | Dice et al. Foster et al.           |                                                                 | ng Circuits", Univ                                                                                                                                                  | -        |                      | Amherst, MA      |  |  |

| 2008/0184038                 |               | 7/2008            |                                     |                                                                 | EE 978-1-4244-645                                                                                                                                                   |          |                      | . II             |  |  |

| 2008/0276092                 |               |                   | Eberhardt et al.                    |                                                                 | al; "Cryptographic<br> 2know System", <                                                                                                                             |          |                      |                  |  |  |

| 2008/0282345<br>2009/0031135 |               | 1/2008            | Kothandaraman                       |                                                                 | mber= $1594225 > or$                                                                                                                                                |          |                      |                  |  |  |

| 2009/0055637                 |               |                   | Holm et al.                         |                                                                 | et al; "An Architec                                                                                                                                                 |          |                      |                  |  |  |

| 2009/0138699                 |               |                   | Miyazaki et al.                     |                                                                 | sting of Multiple                                                                                                                                                   |          |                      |                  |  |  |

| 2009/0150546<br>2009/0150662 |               | 6/2009<br>6/2009  | Desselle et al.                     |                                                                 | summary?doi=10.1<br>onal Search Report                                                                                                                              |          | * *                  |                  |  |  |

| 2009/0154705                 |               |                   | Price et al.                        |                                                                 | ion No. PCT/US20                                                                                                                                                    |          | -                    |                  |  |  |

| 2009/0172496                 |               | 7/2009            |                                     |                                                                 | onal Search Report                                                                                                                                                  |          |                      |                  |  |  |

| 2009/0196418<br>2009/0259854 |               |                   | Tkacik et al.<br>Cox et al.         | Applicat                                                        | ion No. PCT/US20                                                                                                                                                    | 11/066   | 750, mailed on Sep   | 5. 20, 2012, 10  |  |  |

| 2009/0262940                 |               | 10/2009           |                                     | pgs.                                                            | and Casab Danast                                                                                                                                                    |          | Voittan Oninian na   | animad in DCT    |  |  |

| 2009/0271619                 |               |                   | Fujii et al.                        |                                                                 | onal Search Report<br>ion No. PCT/US201                                                                                                                             |          |                      |                  |  |  |

| 2009/0276617<br>2009/0290712 |               |                   | Grell et al.<br>Henry et al.        | ~ ~                                                             | onal Search Report                                                                                                                                                  |          |                      |                  |  |  |

| 2009/0292732                 |               |                   | Manolescu et al.                    |                                                                 | ion No. PCT/US20                                                                                                                                                    |          | -                    |                  |  |  |

| 2009/0293130                 |               |                   | Henry et al.                        | pgs.                                                            | 10 10                                                                                                                                                               | 1.7      | ratu o i i           | · I · Dom        |  |  |

| 2009/0328201<br>2010/0037069 |               | 12/2009<br>2/2010 | Jin et al.<br>Deierling et al.      |                                                                 | onal Search Report<br>ion No. PCT/US201                                                                                                                             |          |                      |                  |  |  |

| 2010/0057960                 | A1            | 3/2010            | Renno                               |                                                                 | onal Search Report                                                                                                                                                  |          |                      |                  |  |  |

| 2010/0064125                 |               |                   | Liu et al.                          |                                                                 | ion No. PCT/US201                                                                                                                                                   |          |                      |                  |  |  |

| 2010/0077226<br>2010/0088739 |               | 3/2010<br>4/2010  | Hall et al.                         |                                                                 | onal Search Report                                                                                                                                                  |          |                      |                  |  |  |

| 2010/0268942                 |               | 10/2010           | Hernandez-Ardieta et al.            | Applicat                                                        | ion No. PCT/US201<br>onal Search Report                                                                                                                             | 12/031   | 542, mailed Sep. 2   | 7, 2012, 9 pgs.  |  |  |

| 2010/0312940<br>2011/0012709 |               | 1/2010            | Shinohara<br>Payson et al.          |                                                                 | ion No. PCT/US20                                                                                                                                                    |          |                      |                  |  |  |

| 2011/0012/09                 |               |                   | Perronnin et al.                    |                                                                 | crosystems, "Sun                                                                                                                                                    |          |                      |                  |  |  |

| 2011/0095776                 | A1            | 4/2011            | Yunoki                              | Firmwar                                                         | e Version 1.1, FIPS                                                                                                                                                 | 140-2    | Non-Proprietary, S   | Security Policy, |  |  |

| 2011/0116635<br>2011/0154501 |               | 5/2011            | Bar-el<br>Banginwar                 |                                                                 | alidation, Aug. 6, 20                                                                                                                                               | ,        |                      | n/technetwork/   |  |  |

| 2011/0134301                 |               |                   | Haga et al.                         |                                                                 | curity/140sp457-16<br>al; "Improving Mer                                                                                                                            |          |                      | ance in Secure   |  |  |

| 2011/0302638                 | A1*           |                   | Cha et al 726/6                     | Processo                                                        |                                                                                                                                                                     |          | ieeexplore.ieee.org  |                  |  |  |

| 2012/0185636                 |               | 7/2012            |                                     |                                                                 | mber= $1407851 > 0$                                                                                                                                                 | n pp.    | 630-640; vol. 54;    | Issue 5, May     |  |  |

| 2012/0224691<br>2012/0246432 |               |                   | Purohit<br>Hadley et al.            | 2005.                                                           | I: 55Th - II                                                                                                                                                        |          | 1 NT1 C+             | M                |  |  |

| 2012/0326692                 |               |                   | Koizumi et al.                      | Addressi                                                        | Learning, "The Hearning," May 16,                                                                                                                                   |          | •                    | •                |  |  |

| 2013/0024637                 |               |                   | Hadley                              |                                                                 | 6210838/http://coll                                                                                                                                                 |          |                      |                  |  |  |

| 2013/0024716                 |               |                   | Hadley                              | ogy_edu                                                         | cation/andrews_97                                                                                                                                                   | 781435   | 5497788/unprotecte   | ed/book          |  |  |

| 2013/0031290<br>2013/0305380 |               | 1/2013            | Schwartz et al.<br>Diehl            |                                                                 | e_Hexadecimial_N                                                                                                                                                    | Jumbe    | r_System_and_N       | 1emory_          |  |  |

| 2014/0115698                 |               |                   | Jogand-Coulomb et al.               | Addressi                                                        | ng.pd1>.<br>iith, "Authentication                                                                                                                                   | n" (av   | cornt) Eab 2002      | http://waxay     |  |  |

| 2014/0130189                 |               |                   | Hadley                              |                                                                 | /crypto/>.                                                                                                                                                          | п, (сл   | (ecipi), 1 co. 2002. | 'shup.// www.    |  |  |

| 2014/0140512<br>2014/0149729 |               |                   | Hadley 713/1                        |                                                                 | m, "Design of a mu                                                                                                                                                  | ltichar  | nnel temperature da  | ata logger with  |  |  |

| 2014/0156961                 |               |                   | Hadley 713/1                        |                                                                 | storage," Electron                                                                                                                                                  |          |                      |                  |  |  |

| 2014/0165206                 | $\mathbf{A}1$ | 6/2014            | Hadley                              |                                                                 | om/downloads/get/<br>et al., "An inexpens                                                                                                                           |          |                      |                  |  |  |

| 2014/0358949                 | A1            | 12/2014           | Hu                                  |                                                                 | , .                                                                                                                                                                 | ,        |                      | , , ,            |  |  |

| FOREIGN PATENT DOCUMENTS     |               |                   |                                     |                                                                 | system," Computers & Geosciences, 2000, vol. 26, pp. 1059-1066. Extended European Search Report, Feb. 5, 2015, European Patent Application No. 12814537.2, 6 pages. |          |                      |                  |  |  |

| CN 1886939 A 12/2006         |               |                   |                                     | Hobbizine, "adding memory with i2c eeproms," May 16, 2010, (web |                                                                                                                                                                     |          |                      |                  |  |  |

|                              |               | 353 A             | 2/2008                              |                                                                 | nttp://picaxe.hobbiz<br>Logger Shield: Data                                                                                                                         |          |                      | eh nage). May    |  |  |

|                              |               | 5012 A<br>3538 A  | 5/2009<br>7/2009                    |                                                                 | , <http: td="" www.ladya<=""><td></td><td>-</td><td></td></http:>                                                                                                   |          | -                    |                  |  |  |

| CN                           | 101995        | 301               | 3/2011                              | Machine                                                         | Translation of Koiz                                                                                                                                                 | zumi e   | t al. (WO2011/080    |                  |  |  |

| EP                           | 0987          | 625               | 3/2000                              | via Goog                                                        | gle Translate on Ma                                                                                                                                                 | r. 23, 2 | 2015.                |                  |  |  |

#### (56) References Cited

#### OTHER PUBLICATIONS

Maxim Integrated Products, "DS1678 Real-Time Event Recorder," 2005, <a href="http://datasheets.maximintegrated.com/en/ds/DS1678.pdf">http://datasheets.maximintegrated.com/en/ds/DS1678.pdf</a>>. Microsoft Corp., "BitLocker Drive Encryption: Scenarios, User Experience, and Flow," May 16, 2006, available at: <a href="http://msdn.microsoft.com/en-us/library/windows/hardware/gg463165.aspx">http://msdn.microsoft.com/en-us/library/windows/hardware/gg463165.aspx</a>>. Microsoft Corp., "BitLocker Drive Encryption: Technical Overview," May 16, 2006.

Microsoft, "How To: Configure MachineKey in ASP.NET 2.0," available Mar. 9, 2012, <a href="http://msdn.microsoft.com/en-us/library/ff649308.aspx">http://msdn.microsoft.com/en-us/library/ff649308.aspx</a>.

National Institute of Standards and Technology, "Security Requirements for Cryptographic Modules," FIPS PUB 140-2, May 25, 2001, <a href="http://csrc.nist.gov/publications/fips/fips140-2/fips1402.pdf">http://csrc.nist.gov/publications/fips/fips140-2/fips1402.pdf</a>>.

National Institute of Standards and Technology, "Security Requirements for Cryptographic Modules," FIPS PUB 140-3, Draft, p. 16, Sep. 11, 2009, and Annexes A-G <a href="http://csrc.nist.gov/publications/PubsDrafts.html#FIPS-140">http://csrc.nist.gov/publications/PubsDrafts.html#FIPS-140</a>—3>.

Raafat. S. Habeeb, "Design a Programmable Sequence Controller Utilizing I2C BUS," 2011, Journal of Madenat Alelem College, vol.

3, iss. 2, pp. 5-25, <a href="http://www.iasj.net/iasj?func=fulltext">http://www.iasj.net/iasj?func=fulltext</a> &ald=60778>.

Revolution Education Ltd., "Picaxe Datalogger (AXE110P)," version 2.0, (web page), Dec. 2010, <a href="http://www.picaxe.com/docs/axe110.pdf">http://www.picaxe.com/docs/axe110.pdf</a>>.

Supplementary European Search Report, Apr. 22, 2015, European Patent Application No. 11869688.9, 6 pages.

ViaSat, Inc., "Requirements Description for an Advanced Cryptographic Module (ACM) to Support the High Capacity Communications Capability (HC3)," Technical Report, Oct. 18, 2005, <a href="http://cryptome.org/acm-hc3.htm">http://cryptome.org/acm-hc3.htm</a>.

Yang, et al; "Improving Memory Encryption Performance in Secure Processors", <a href="http://ieeexplore.ieee.org/stamp/stamp.">http://ieeexplore.ieee.org/stamp/stamp.</a> jsp?arnumber=1407851 > On pp. 630-640; vol. 54; Issue: 5, May, 2005

Yao, et al.; "Calibrating On-chip Thermal Sensors in Integrated Circuits: A Design-for-Calibration Approach", Springer Science+Business Media, LLC 2011, Sep. 21, 2011.

Supplementary Partial European Search Report, European Patent Application No. 12814434.2, Jan. 28, 2016, 10 pages.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

#### SECURE BOOT INFORMATION WITH VALIDATION CONTROL DATA SPECIFYING A VALIDATION TECHNIQUE

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims priority to U.S. provisional patent application No. 61/509,078, filed on Jul. 18, 2011, which is hereby incorporated by reference herein in its entirety.

#### **BACKGROUND**

A computing device, such as a device including a processor, may interact with secret or otherwise sensitive information during operation. As such, some computing devices may operate to protect the sensitive information. For example, a computing device may encrypt sensitive information using a security parameter, such as an encryption key, stored on the device. The computing device may also operate to protect the security parameter stored on the device.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The following detailed description references the draw- 25 ings, wherein:

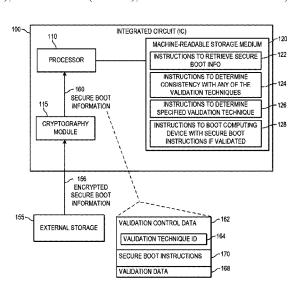

FIG. 1 is a block diagram of an example integrated circuit (IC) to validate secure boot information with a validation technique specified in the secure boot information;

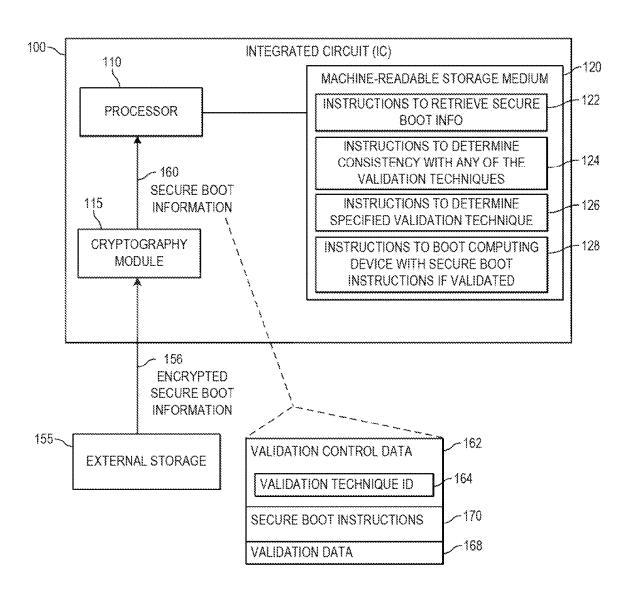

FIG. **2** is a block diagram of an example computing device <sup>30</sup> comprising an IC to determine a validation technique specified in secure boot information;

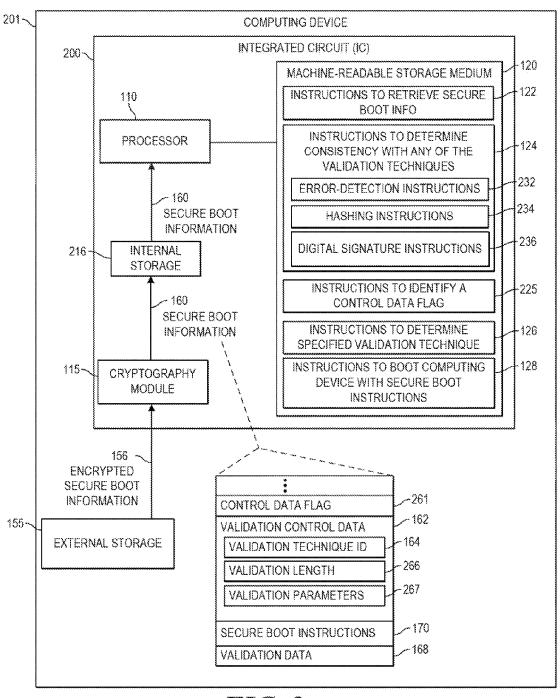

FIG. 3 is a block diagram of an example IC to decrypt and validate secure boot information stored in external storage;

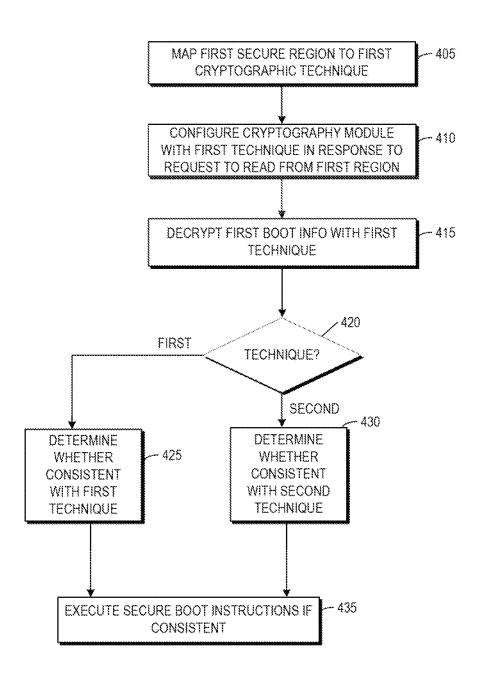

FIG. 4 is a flowchart of an example method for generating 35 test validation data with a validation technique specified in validation control data; and

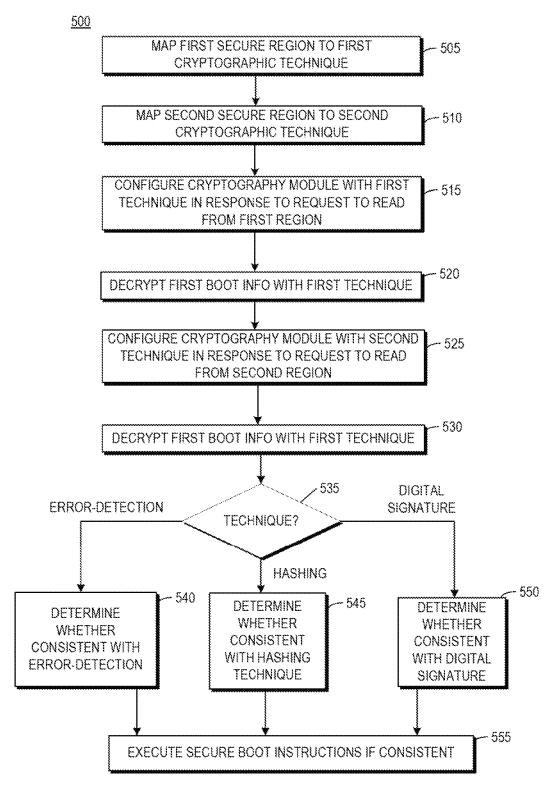

FIG. 5 is a flowchart of an example method for decrypting secure boot information with at least one cryptographic technique and a specified validation technique.

#### DETAILED DESCRIPTION

As noted above, a computing device may operate to protect sensitive information using security parameters stored on the computing device. To protect both the sensitive information and the security parameters, an integrated circuit (IC) of a computing device may have multiple operating states that may each be utilized in different stages of the life cycle of the computing device. For example, when a computing device is 50 being developed, tested, and/or initialized in a controlled environment, the IC may be operated in a clear state in which the IC provides little or no security for information stored on or utilized by the IC. For example, boot instructions executed by the IC in this clear state may be stored outside the processor in a cleartext (e.g., unencrypted, uncompressed, etc.) format.

When the computing device is operated in an environment in which it is vulnerable to security threats, the IC may be operated in a secure state in which the device may provide 60 more security for information stored on or utilized by the IC than in the clear state. For example, secure boot information used to boot the computing device in the secure state may be stored outside of the IC in an encoded (e.g., encrypted) format to prevent an unauthorized party from determining the content of the information and tampering with the information to gain access to security parameters stored on the IC. Addition-

2

ally, in response to a breach of the computing device's security, the IC may zeroize its security parameters and operate thereafter in a zeroize state in which the IC provides event reporting and diagnostic functionalities until the device is returned to the controlled environment.

To provide additional security for the secure state, an IC may perform an integrity check with a predefined validation technique to validate the integrity of the secure boot information stored outside of the IC prior to using the information (e.g., executing instructions). Different validation techniques provide different tradeoffs in complexity, speed, and security, so one validation technique may not be suitable or desirable for every context. For example, a fast, relatively simple validity check may be suitable for a computing device for which there is a relatively low risk of security threats. However, a more complex, more secure, slower validation technique may be desired for a computing device that, for example, is more vulnerable to security threats, that uses more sensitive information, etc. Additionally, a computing device may not meet certain security standards (e.g., government-imposed security standards) unless a particular validation technique is used.

To address these issues, in examples disclosed herein, an IC may verify the validity of secure boot information stored external to the IC by retrieving the secure boot information, determining a validation technique specified in the secure boot information, and verifying the integrity of the secure boot information with the specified validation technique. In such examples, the IC may be capable of using any one of a plurality of different validation techniques to validate the secure boot information. In this manner, examples disclosed herein may provide a single IC that may be used in a variety of contexts regardless of a desired validation technique. Additionally, by allowing a desired validation technique to be specified in the information to be validated, examples disclosed herein may provide much flexibility for the manner of validating information integrity. For example, as security threats or standards change, examples disclosed herein may allow the validation technique used by an IC to be readily changed by changing the validation technique specified in the information to be validated.

Referring now to the drawings. FIG. 1 is a block diagram of an example integrated circuit (IC) 100 to validate secure boot information with a validation technique specified in the secure boot information. In the example of FIG. 1, IC 100 includes a processor 110, a cryptography module 115, a machine-readable storage medium 120 including (e.g., encoded with) instructions 122, 124, 126, and 128. In some examples, storage medium 120 may include additional instructions. In other examples, instructions 122, 124, 126, 128, and any other instructions described herein in relation to storage medium 120 may be stored remotely from IC 100. In some examples, IC 100 may be included in a computing device. As used herein, a "computing device" may be a desktop or notebook computer, a tablet computer, a computer networking device (e.g., a hardware security module), a server, or any other device or equipment (e.g., an automated teller machine (ATM), etc.) including a processor.

As used herein, a "processor" may be electronic circuitry including at least one of a central processing unit (CPU), a graphics processing unit (GPU), a field-programmable gate array (FPGA) configured to retrieve and execute instructions stored on a machine-readable storage medium, other electronic circuitry suitable for the retrieval and execution of such instructions, or a combination thereof. Processor 110 may fetch, decode, and execute instructions stored on storage medium 120 to implement the functionalities described

below. In other examples, the functionalities of any of the instructions of storage medium 120 may be implemented in the form of electronic circuitry, in the form of executable instructions encoded on a machine-readable storage medium, or a combination thereof.

Additionally, as used herein, a "machine-readable storage medium" may be any electronic, magnetic, optical, or other physical storage device to contain or store information such as executable instructions, data, and the like. For example, any machine-readable storage medium described herein may be any of Random Access Memory (RAM), flash memory, a storage drive (e.g., a hard disk), a Compact Disc Read Only Memory (CD-ROM), and the like, or a combination thereof. Further, any machine-readable storage medium described herein may be non-transitory.

In some examples, instructions 122 may retrieve, with processor 110, secure boot information 156 from external storage 155. In examples described herein, external storage 155 may be a machine-readable storage medium. In some 20 examples, external storage 155 may be external to IC 100. In the example of FIG. 1, instructions 122 may cause processor 110 to retrieve secure boot information 156 via cryptography module 115 to decrypt secure boot information 156, which may be stored in an encrypted format in external storage 155. 25 In some examples, instructions 122 may retrieve secure boot information 156 beginning at a secure reset vector. As used herein, a "reset vector" may be an address from which a processor may first retrieve information after undergoing a reset. In some examples, IC 100 may include multiple reset 30 vectors. For example, a "secure reset vector" may be a reset vector used after a reset in a secure state, a "clear reset vector" may be a reset vector used after a reset in clear state, and a "zeroize reset vector" may be a reset vector used after a reset in zeroize state.

As used herein, a "cryptography module" is a module implementing at least one information formatting technique and that may reformat input information with any one of the formatting techniques. Example information formatting techniques that may be implemented by a cryptography module 40 include, for example, encryption and/or decryption techniques, compression and/or decompression techniques, and any other information encoding and/or decoding techniques. In some examples, a cryptography module may implement a plurality of different formatting techniques and reformat 45 input information with a selected one of the formatting techniques. Any cryptography module described herein may be implemented in the form of electronic circuitry, in the form of executable instructions encoded on a machine-readable storage medium, or a combination thereof.

Additionally, as used herein, "boot information" is information that may be used by a processor of a computing device to boot the computing device. In some examples, the boot information may include at least one of boot data (e.g., addresses and/or other information, etc.) and boot instruc- 55 tions. As used herein. "boot instructions" are a set of instructions that may be executed by a processor of a computing device to boot the computing device. Boot instructions may include, for example, instructions to test and/or configure components and/or functionalities of the computing device. 60 In such examples, computing device components that may be tested and/or configured may include a processor, memory, a memory management unit, cryptographic functionalities, and the like, or a combination thereof. Also, as used herein, "secure boot information" may be boot information used to 65 boot a computing device in a secure mode of operation. In some examples, secure boot information may include secure

4

boot instructions, which may be boot instructions used to boot a computing device in a secure mode of operation.

In some examples, instructions 122, when executed, may cause processor 110 to provide at least one read request to external storage 155 (e.g., via an external bus controller) to retrieve secure boot information 156. In response to the at least one read request, external storage 155 may provide encrypted secure boot information 156 to cryptography module 115 (e.g. via the external bus controller). In such examples, cryptography module 115 may decrypt the encrypted secure boot information 156 to generate decrypted secure boot information 160, which may be in a cleartext format. In some examples, in response to the read request, a memory management unit may configure cryptography module 115 with cryptographic information corresponding to the memory region targeted in the read request, such as a cryptographic technique, a cryptographic key, or the like. In such examples, cryptography module 115 may use this cryptographic information to decrypt information read from storage 155. In some examples, cryptography module 115 may provide decrypted secure boot information 160 to an internal storage at which processor 110 may access secure boot information 160. In other examples, cryptography module 115 may provide decrypted secure boot information 160 to processor 110 without first providing the secure boot information 160 to internal storage. In such examples, processor 110 may store the received decrypted secure boot information 160 in internal storage (e.g., cache).

As used herein, information in a "cleartext" format for a given computing device is information that a processor of the computing device is able to execute or otherwise operate on without first reformatting (e.g., decrypting, decoding, etc.) the information. For example, instructions in a cleartext format may be instructions that the processor may execute without first reformatting the instructions. Information in a cleartext format may also be referred to herein as "decrypted" information. As used herein, information in an "encrypted" format for a given computing device is information in a format that a processor of the computing device may execute or otherwise operate on after the information is decrypted.

In the example of FIG. 1, secure boot information 160 may include validation control data 162, secure boot instructions 170, and validation data 168 for secure boot information 160. As used herein, "validation data" for a collection of information is data derived from the collection of information at a given point in time that may be used subsequently to determine whether the information (or a particular portion thereof) has changed since the generation of the validation data. In some examples, validation data for a collection of information may be, for example, a digest, a code, a hash, a digital signature, or the like, derived from at least a portion of the information. In some examples, validation control data 162 may be located at or near the beginning of secure boot information 160. In other examples, validation control data 162 may be located at any other location within secure boot information 160. Additionally, in the example of FIG. 1, validation data 168 is separate from validation control data 162. In some examples, validation data 168 may be located at or near the end of secure boot information 160. In other examples, validation data 168 may be located elsewhere in secure boot information 160. In other examples, validation control data 162 may include validation data 168. In some examples, encrypted secure boot information 156 may comprise secure boot information **160** in an encrypted format.

Storage medium 120 further comprises instructions 124 to determine, with any one of a plurality of different validation techniques, whether validation data 168 is consistent with the

decrypted secure boot information 160. In such examples, instructions 124 may determine whether validation data 168 is consistent with secure boot information 160 using whichever of the plurality of validation techniques is specified in secure boot information 160. As used herein, a "validation 5 technique" is a process for determining whether given validation data is consistent with a given collection of information. Additionally, as used herein, validation data "is consistent with" a collection of information for a given validation technique if test data derived from at least a portion of the 10 information as part of the validation technique is equivalent to the validation data or data derived from the validation data as part of the validation technique.

5

In the example of FIG. 1, instructions 124 may utilize any one of a plurality of different validation techniques to determine whether validation data 168 is consistent with the decrypted secure boot information 160. In some examples, instructions 124 may include instructions to perform each of the plurality of different validation techniques. In other examples, instructions 124 may include instructions to utilize 20 a cryptography module to perform each of the different validation techniques.

As used herein, validation techniques are "different" if they use different processes for determining whether validation data for a collection of information is consistent with the 25 information. In some examples, validation techniques using different functions for deriving the test data from given information may be considered different validation techniques herein. For example, two hash validation techniques using different hash functions, respectively, to derive test data from 30 a given set of information may be considered different validation techniques herein. Another example of different validation techniques may be an error-detection validation technique and a hash validating technique using different functions for deriving test data from a given collection of 35 information. In other examples, validation techniques using different processes after deriving the test data may be considered different validation techniques herein. For example, a hash validation technique may determine that given validation data is consistent with given information if the validation 40 data is equivalent to test data derived from the information using a hash function. However, a different digital signature validation technique may determine that the validation data is consistent with the given information if test data derived from the information is equivalent to other data derived by decrypt- 45 ing the validation data with a public key.

In the example of FIG. 1, instructions 126 may determine which of the plurality of different validation techniques is specified in validation control data 162 of secure boot information 160. For example, validation control data 162 may 50 include a validation technique identifier 164. In such examples, instructions 126 may determine the specified validation technique of the plurality of validation techniques based on validation technique identifier 164.

In the example of FIG. 1, instructions 124 may determine 55 whether validation data 168 is consistent with decrypted secure boot information 160 with the validation technique specified by identifier 164. In some examples, instructions 124 may determine, with the specified validation technique, whether validation data 168 is consistent with decrypted 60 secure boot information 160 after all of secure boot information 156 is retrieved from external storage 155. In such examples, instructions 124 may cause test data to be derived from at least a portion of secure boot information 160 stored in internal memory of IC 100. In other examples, instructions 65 124 may determine, with the specified validation technique, whether validation data 168 is consistent with decrypted

6

secure boot information 160 at least partially in parallel with retrieving secure boot information 156. For example, after retrieving and decrypting the portion of secure boot information 160 including validation control data 162, instructions 126 may determine the specified validation technique. In such examples, instructions 124 may begin deriving the test data from portions of secure boot information 160 output by cryptography module 115 before all of secure boot information 156 is retrieved from external storage 155. In such examples, instructions 124 may continue deriving the test data as the encrypted secure boot information 156 is retrieved and decrypted. In some examples, instructions 124 may derive the test data from information 160 output by cryptography module 115 before, after, or at least partially in parallel with information 160 being stored in internal storage of IC 100. In other examples, instructions 124 may derive the test data from information 160 output by cryptography module 115 before or at least partially in parallel with information 160 being encrypted again by cryptography module 115 and stored in other storage external to IC 100 (e.g., an external DRAM).

In some examples, instructions 128 may boot a computing device including IC 100 with secure boot instructions 170 if it is determined, with the validation technique specified by identifier 164 of control data 162, that validation data 168 is consistent with the decrypted secure boot information 160. As noted above, secure boot information 160 output by cryptography module 115 may be stored in internal storage (e.g., cache) of IC 100. In some examples, instructions 128 may boot the computing device with secure boot instructions 170 by causing processor 110 to jump to secure boot instructions 170 stored in the internal memory, or by otherwise transferring control to secure boot instructions 170 stored in the internal memory. In other examples, in response to determining that validation data 168 is consistent with secure boot information 160, instructions 128 may trigger the execution of secure boot instructions 170 stored in external storage 155. In such examples, instructions 128 may trigger the retrieval of at least secure boot instructions 170 via cryptography module 115 and the execution of the received secure boot instructions 170 without validating the retrieved information again. In other examples, instructions 128 may trigger the retrieval of at least secure boot instructions 170 stored in the other external storage (e.g., external DRAM) via cryptography module 115 and the execution of the received secure boot instructions 170 without validating the retrieved information again.

Examples described herein provide the ability to validate secure boot information using any one of a plurality of different validations techniques. In examples described herein, secure boot information retrieved from external storage may be validated using a validation technique specified in validation control data of the secure boot information. In this manner, examples disclosed herein may provide flexibility in the validation of information retrieved from external storage by implementing a plurality of different validation techniques and allowing a validation technique for validating a given collection of information to be specified in the information to be validated. In some examples, functionalities described herein in relation to FIG. 1 may be provided in combination with functionalities described herein in relation to any of FIGS. 2-5.

FIG. 2 is a block diagram of an example computing device 201 comprising an IC 200 to determine a validation technique specified in secure boot information. In the example of FIG. 2, IC 200 may include a processor 110, a cryptography module 115, and a machine-readable storage medium 120, as described above in relation to FIG. 1. Storage medium 120 may include instructions 232, 234, 236, and 225, in addition

to instructions 122, 124, 126, and 128 described above in relation to FIG. 1. IC 200 may also include internal storage 216, which may be a machine-readable storage medium. In addition to IC 200, computing device 201 may also include external storage 155, as described above in relation to FIG. 1. 5 In other examples, external storage 155 may be remote from IC 200 and computing device 201.

In the example of FIG. 2, instructions 122, when executed, may cause processor 110 to retrieve secure boot information 156 from external storage 155 via cryptography module 115 to decrypt secure boot instructions 156 to generate decrypted secure boot information 160, as described above in relation to FIG. 1. In the example of FIG. 2, cryptography module 160 may store decrypted secure boot information 160 in internal storage 216. In such examples, processor 110 may access 15 decrypted secure boot information 160 stored in internal storage 216

In the example of FIG. 2, instructions 124 may determine whether validation data 168 of secure boot information 160 is consistent with secure boot information 160 with any one of 20 a plurality of different validation techniques, as described above in relation to FIG. 1. In some examples, instructions 124 may derive test data from at least a portion of secure boot information 160 in accordance with the specified validation technique and determine whether the derived test data is 25 equivalent to validation data 168 or data derived from validation data 168 as part of the specified validation technique.

In the example of FIG. 2, validation control data 162 may include a validation length 266. In such examples, instructions 124 may comprise instructions to derive the test data 30 from a portion of decrypted secure boot information 160 having a length equal to validation length 266. For example, if instructions 124 derive the test data from information 160 using a hashing function, then instructions 124 may derive the test data by performing the hashing function on a portion of 35 information 160 having a length equal to validation length 266, such as the first portion of information 160 having validation length 266. In other examples, the test data may be derived from the entire length of information 160, excluding validation data 168, for example.

In some examples, validation control data 162 may also include at least one validation parameter 267 for the validation technique specified by validation technique identifier 164. Validation parameters 267 may include, for example, at least one of an initialization value for a process for deriving 45 test data from secure boot information (e.g. a cyclic redundancy check (CRC) technique), a public key used in a digital signature validation technique, the length of the public key, an indication of whether the public key is included in validation control data 162, and any other parameters that may be used 50 by the validation technique specified by identifier 164. In examples in which the public key is not included in validation control data 162, the public key may be stored in IC 200.

In the example of FIG. 2, instructions 124 may include instructions to perform each of the plurality of different validation techniques to determine whether validation data 168 of secure boot information 160 is consistent with secure boot information 160. In some examples, instructions 124 may include instructions 232 to determine, with an error-detection validation technique, whether validation data 168 is consistent with decrypted secure boot information 160. In examples described herein, an error-detection validation technique may be a validation technique in which the test data is derived from a given collection of information by an error-detection process, such as a checksum process, a cyclic redundancy check (CRC) process, or any other suitable error-detection process. In such examples, an error-detection validation technique

8

may determine that given validation data is consistent with the given information if the test data derived with the errordetection process is equivalent to the validation data. In some examples, instructions 232 may include a plurality of different error-detection validation techniques, each deriving the test data with a different error-detection process.

Instructions 124 may also include instructions 234 to determine, with a hashing validation technique, whether validation data 168 is consistent with decrypted secure boot information 160. In examples described herein, a hashing validation technique may be a validation technique in which the test data is derived from a given collection of information by performing a hash function on (i.e., hashing) at least a portion of the information. In such examples, a hashing validation technique may determine that given validation data is consistent with the given information if the test data derived by performing the hash function on the given information is equivalent to the validation data. In some examples, instructions 234 may include a plurality of different hashing validation techniques, each deriving the test data with a different hash function. Example hash functions may include, for example, cryptographic hash functions (e.g., SHA-256, SHA-512, etc.), noncryptographic hash functions (e.g., FNV hash, etc.), or any other hash function.

Additionally, instructions 124 may include instructions 236 to determine, with a digital signature validation technique, whether validation data 168 is consistent with decrypted secure boot information 160. In examples described herein, a digital signature validation technique may be a validation technique in which test data is derived from given information by hashing at least a portion of the information and decrypted data is derived from given validation data by decrypting the validation data. In such examples, a digital signature validation technique may determine that the given validation data is consistent with the given information if the test data is equivalent to the decrypted data derived from the validation data. In some examples, instructions 236 may include a plurality of different digital signature validation techniques, each differing in at least one of a hash function for deriving test data, a decryption process, etc. Example digital signature validation techniques may include techniques based on, for example, an RSA/PKCS based technique, a federal information processing standard (FIPS) digital signature algorithm (DSA), a elliptic curve digital signature algorithm (ECDSA), an Elgamal signature technique, or any other digital signature technique.

In the example of FIG. 2, instructions 126 may determine which of the plurality of different validation techniques is specified by validation technique identifier 164 of validation control data 162 of secure boot information 160, as described above in relation to FIG. 1. In some examples, validation control data 162 may be located at any location within secure boot information 160. In such examples, secure boot information 160 may include a control data flag 261 in addition to validation control data 162, secure boot instructions 170, and validation data 168, as described above in relation to FIG. 1. Control data flag 261 may be any information indicating the location of validation control data 162 in decrypted secure boot information 160. For example, control data flag 261 may be a particular bit-mask, data pattern, or other information reserved for flag 261 and known by instructions 225. In such examples, instructions 225 may identify control data flag 261 in decrypted secure boot information 160 output from module 115.

In some examples, instructions 225 may use the location of flag 261 to determine the location of validation control data 162. For example, secure boot information 160 may be orga-

nized such that validation control data 162 directly follows flag 261 in secure boot information 160 or is located at another predefined location relative to flag 261 within information 160. In such examples, after instructions 225 identify the location of validation control techniques, instructions 126 may determine which of the plurality of different validation techniques is specified by validation technique identifier 164 of validation control data 162, as described above in relation to FIG. 1.

In other examples, secure boot information 160 may be 10 organized such that validation control data 162 has a constant location in secure boot information 160. In such examples, flag 261 and instructions 225 may be omitted, and instructions 126 may look to the constant location within secure boot information 160 to find validation control data 162. For 15 example, validation control data 162 may be located at a predefined offset within secure boot information 160. In such examples, instructions 126 may determine the specified validation technique from the validation technique identifier 164 of the validation control data 162 at the constant location 20 within secure boot information 160. For example, validation control data 162 may start at a first location of secure boot information 160, or any other location in secure boot information 160.

In the example of FIG. 2, after instructions 126 determine 25 the validation technique specified in validation control data 162, instructions 124 may determine whether validation data 168 is consistent with secure boot information 160 using whichever of the plurality of the validation techniques is specified by validation technique identifier **164** of validation 30 control data 162. In some examples, instructions 124 may determine, with the specified validation technique, whether validation data 168 is consistent with decrypted secure boot information 160 at least partially in parallel with retrieving secure boot information 156, as described above in relation to 35 FIG. 1. If instructions 124 determine that validation data 168 is not consistent with secure boot information 160, then instructions 124 may output an alarm and not boot computing device 201. The alarm may be output by instructions 124 on at least one status indicator (e.g., lights) of computing device 40 201 connected to IC 200.

In some examples, instructions 128 may boot computing device 201 with secure boot instructions 170 if it is determined, with the validation technique specified by identifier secure boot information 160, as described above in relation to FIG. 1. In some examples, instructions 128 may trigger execution of secure boot instructions 170 by processor 110 if validation data 168 is determined to be consistent with information 160. In the example of FIG. 2, secure boot information 50 160 may be stored in internal storage 216. In such examples, instructions 128 may boot computing device 201 with instructions 170 by triggering execution, by processor 110, of secure boot instructions 170 stored on internal storage 216 if validation data 168 is consistent with decrypted secure boot 55 information 160. In such examples, instructions 128 may cause processor 110 to jump to instructions 170 on internal storage 216, or otherwise transfer control to instructions 170. In other examples, instructions 128 may cause processor 110 to retrieve and execute instructions 170 from external storage 60 155 if validation data 168 is consistent with decrypted secure boot information 160. In other examples, secure boot information stored in internal storage 216 may be encrypted again by cryptography module 115 and stored in other storage external to IC 100, such as an external DRAM, if validation 65 data 168 is consistent with decrypted secure boot information 160. In such examples, instructions 128 may cause processor

10

110 to retrieve and execute instructions 170 from the other external storage (e.g., external DRAM). In some examples, functionalities described herein in relation to FIGS. 1-2 may be provided in combination with functionalities described herein in relation to any of FIGS. 3-5.

FIG. 3 is a block diagram of an example computing system 395 including an IC 300 to decrypt and validate secure boot information stored in external storage 155. In the example of FIG. 3, computing system 395 includes IC 300 and external storage 155. IC 300 includes a processor 310 and internal storage 320 including (e.g., encoded with) a set of executable internal instructions 321, including instructions 322, 324, 326, 328, and 332. Internal storage 320 may be a machinereadable storage medium. Processor 310 may fetch, decode, and execute instructions stored on internal storage 320 to implement the functionalities described below. In other examples, the functionalities of any of the instructions of internal storage 320 may be implemented in the form of electronic circuitry, in the form of executable instructions encoded on a machine-readable storage medium, or a combination thereof.

IC 300 may also include a cryptography module 115, as described above in relation to FIG. 1, a cryptography module 314, a memory management unit 318, and secure storage 370. In some examples, memory management unit 318 may be implemented in the form of electronic circuitry, in the form of executable instructions encoded on a machine-readable storage medium, or a combination thereof. Secure storage 370 may be a machine-readable storage medium. Additionally, in some examples, secure storage 370 may be a machine-readable storage medium.

In the example of FIG. 3, processor 310 may execute internal instructions 321 in response to a reset request 381 if, at least, a secure state value is stored in operating state storage 314 of IC 300. In some examples, processor 310 may execute internal instructions 321 in response to a reset request 381 if a secure state value is stored in operating state storage 314 of IC 300. In other examples, processor 310 may execute internal instructions 321 in response to a reset request 381 if a secure state value is stored in operating state storage 314 and a non-validated value is stored in validation result storage 316 of IC 300.

In some examples, internal instructions 321 may be 164, that validation data 168 is consistent with decrypted 45 instructions to validate secure boot instructions prior to executing the secure boot instructions in a secure mode of operation. For example, it may be desirable to validate the integrity of secure boot information 160 prior to executing instructions 170 to provide additional protection for sensitive information and security parameters utilized by a computing device including IC 300. Such validation, which may delay booting, may not be desirable in a clear state primarily used in a secure environment or in a zeroize state in which security parameters have been zeroized and are likely not vulnerable. Accordingly, in some examples, internal instructions 321 may be executed in a secure state, and not in a clear or zeroize

> In the example of FIG. 3, a reset handler 312 of processor 310 may receive reset request 381 and, in response to reset request 381, determine whether to execute internal instructions 321. In such examples, in response to reset request 381, reset handler 312 may determine whether a secure state value (e.g., a value indicating a secure state) is stored in operating state storage 314. In some examples, operating state storage 314 may store a value indicating the state (e.g., secure, clear, zeroize, etc.) in which IC 300 is to operate after reset. For example, if a clear state value or a zeroize state value is stored

in state storage 314, then reset handler 312 may determine not to execute internal instructions 321 in response to reset request 381.